趣味工房 HIRO-G

< ロジックアナライザーLAP-C 購入とテスト計測 >

前回の報告からチマチマと写真1のμPD765Aについて調べました結果、コマンドの動作と制御につきましてある程度理解できるようになり、このトラ技(1984年10月号P421)のDMAコントローラを使用しないDMA転送のユニークな回路とイニシャライズ・プログラム(1985年1月号P462~461)の関係が分かってきました(現在進行形で、完全に理解できたわけではありません。)。 全容を把握するためには、どうしても各コマンドのタイミング信号を計測する必要がありそうです。

今まで避け続けていたタイム・チャートの解析に踏み込まざるをえないようで、ついにその時が来たか!?、の感じで、ロジックアナライザーの調査・検討をしました。 結果、PC接続が必要ですが、当方にとっては高機能過ぎるのですが、価格が手頃な写真2のZEROPLUS社のLAP-C(16128)を購入しました。

この回路に記載されている、DMAモードにおけるデータの転送は、「DRQ信号」が発生するごとに、DACK(-)、RD(-)をアクティブにすることで実行されることを利用するものですが、現状は前回報告しました様に、その機能が働かずBD91H番地でループから抜け出せない状態ではないかと推察しています。

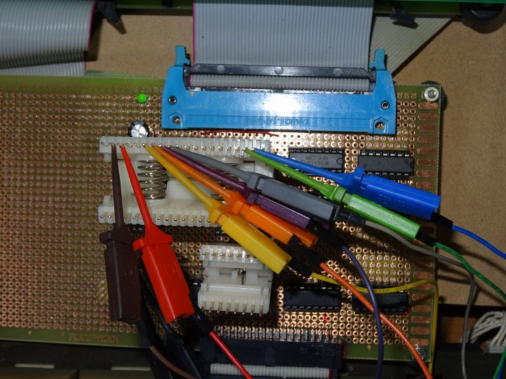

マニュアルが英文のため、スッタモンダしましたが何とか使えるようになりましたので、LAP-Cの操作の練習を兼ねて765Aの動作試験をやってみました。 計測点は次の通りで、写真3は計測用のリード線の状態です。

A0-φ(19P)、 A1-INT(18P)、 A2-DRQ(12P)、

A3-DACK(15P)、 A4-WR(3P)、 A5-RD(2P)

A6-RQM(13P)、 A7-DIO(12P)

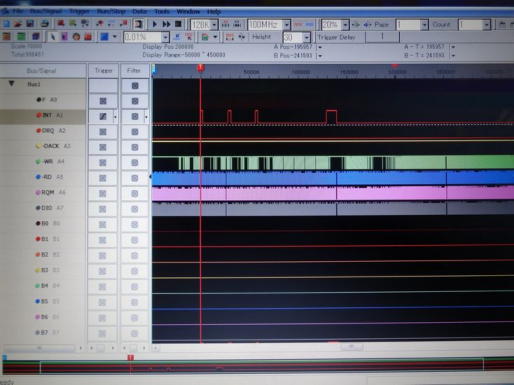

写真4は計測状況の全体で、写真5はμPD765Aの計測点の状態です。 写真6は、計測結果の一例としてINT(18P)をトリガーとして計測した結果ですが、この結果ではINT信号は4回計測されていますが、それ以降計測されておらず、ループに陥っている状況を示しているのではないかと思います。

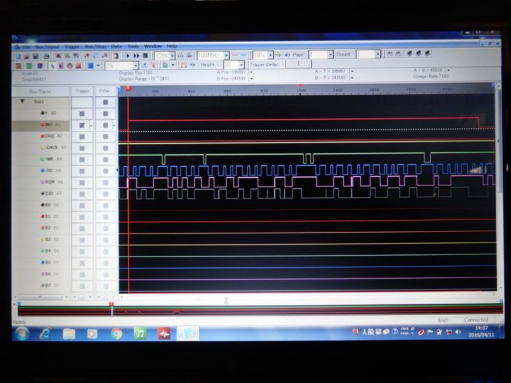

因みに写真7は、他の信号を確認するために、同じ結果の時間軸を拡大したものです。

何とかロジアナが使えるようになりましたので、不具合の原因調査を進めます。

写真1 μPD765A

写真2 LAP-C(16128)

写真3 LAP-C(16128)計測用リード線の状態

< 今後の予定 >

① FDDコントロール・ボードの不具合調査: 調査継続中

② FDDコントロール・ボードのテスト:

③ CP/Mシステム復元の可能性の検討:

④ CP/Mシステム復元作業:

⑤ グラフィック・ボードの製作:

BASIC No61

2016年4月11日 |

|

写真4 計測の状況  写真5 μPD765A計測点の状況  写真6 計測結果の一例  写真7 時間軸を拡大した例 |